產(chǎn)業(yè)觀(guān)察丨如何有效處理電源完整性問(wèn)題?

隨著PCB設(shè)計(jì)復(fù)雜性的增加,信號(hào)完整性的分析不僅包括反射、串?dāng)_及EMI,穩(wěn)定可靠的電源供應(yīng)亦成為研究的關(guān)鍵領(lǐng)域之一。尤其在低壓大電流和高速設(shè)計(jì)供電環(huán)境中,電源的波動(dòng)可能導(dǎo)致嚴(yán)重后果,因此提出了“電源完整性”,即PI(power integrity)的概念。

什么是電源完整性?

在板級(jí)設(shè)計(jì)中,信號(hào)完整性(SI)、電源完整性(PI)以及電磁兼容性(EMC)是三個(gè)核心問(wèn)題。信號(hào)完整性確保數(shù)字電路的正常運(yùn)作及芯片間的有效通信;電源完整性則確保系統(tǒng)具備穩(wěn)定的供電和良好的噪聲抑制能力;電磁干擾(EMI)則關(guān)注PCB板級(jí)電路系統(tǒng)不干擾其他系統(tǒng),同時(shí)也不受其他系統(tǒng)干擾。可以說(shuō),電源完整性是信號(hào)完整性和電磁兼容性的基礎(chǔ)。

電源完整性設(shè)計(jì)涵蓋整個(gè)供電系統(tǒng)的各個(gè)環(huán)節(jié),自電源起始,依次經(jīng)過(guò)濾波電容、PCB走線(xiàn)、過(guò)孔,直至負(fù)載芯片封裝內(nèi)部的die。鑒于實(shí)際電流消耗是在負(fù)載芯片上發(fā)生,電源完整性設(shè)計(jì)不僅包含VRM(電源芯片)、PCB上的電容、PCB上的電源與地平面,還涉及芯片封裝內(nèi)的電容、封裝內(nèi)的電源與地網(wǎng)絡(luò),以及Die上的電容。電源完整性作為一個(gè)系統(tǒng)級(jí)概念,系統(tǒng)中任何細(xì)微的變化均可能對(duì)整體性能產(chǎn)生影響。

PI設(shè)計(jì)的目標(biāo)旨在為負(fù)載芯片提供穩(wěn)定電壓,并確保該電壓能夠保持在極小的容差范圍內(nèi),例如5%或3%的要求。

在理想狀態(tài)下,電源的阻抗應(yīng)為零,從而確保電源網(wǎng)絡(luò)內(nèi)各點(diǎn)的電壓恒定,等同于電源的輸出電壓。但現(xiàn)實(shí)中,電源網(wǎng)絡(luò)往往遭受顯著的噪聲干擾,一旦干擾程度超出一定閾值,便會(huì)對(duì)系統(tǒng)的正常運(yùn)行造成影響。

電源系統(tǒng)的噪聲受多種因素影響,主要包括以下方面:

首先,穩(wěn)壓電源芯片的輸出電壓紋波是開(kāi)關(guān)電源斬波工作模式的固有特性,此類(lèi)噪聲難以避免。盡管線(xiàn)性電源具有較好的輸出紋波特性,且自身輸出噪聲較低,但由于輸出功率有限,轉(zhuǎn)換效率不高,因此在多數(shù)應(yīng)用場(chǎng)景中,仍需選擇開(kāi)關(guān)電源。

其次,穩(wěn)壓電源無(wú)法實(shí)時(shí)響應(yīng)負(fù)載電流變化,導(dǎo)致產(chǎn)生電壓噪聲。穩(wěn)壓電源通過(guò)感知輸出電壓變化,調(diào)整輸出電流,以維持額定電壓值。然而,當(dāng)負(fù)載電流快速變化或穩(wěn)壓電源的環(huán)路設(shè)計(jì)不當(dāng)時(shí),穩(wěn)壓電源無(wú)法及時(shí)提供足夠的電流,輸出電壓將出現(xiàn)上下波動(dòng),進(jìn)而產(chǎn)生電源噪聲。

第三,負(fù)載瞬態(tài)電流在電源路徑和地路徑上產(chǎn)生的電壓降也會(huì)引起電源噪聲。PCB板上的任何電氣路徑均存在阻抗,無(wú)論是完整的電源平面還是電源引線(xiàn)。對(duì)于多層板,通常設(shè)有完整的電源平面和地平面,穩(wěn)壓電源輸出首先接入電源平面,供電電流流經(jīng)電源平面,到達(dá)負(fù)載電源引腳。地路徑與電源路徑類(lèi)似,但電流路徑變?yōu)榈仄矫妗M暾矫娴淖杩馆^低,但并非不存在。若使用引線(xiàn)而非平面,路徑上的阻抗將更高。此外,引腳及焊盤(pán)本身存在寄生電感,瞬態(tài)電流流經(jīng)此路徑必然產(chǎn)生壓降,因此負(fù)載芯片電源引腳處的電壓會(huì)隨瞬態(tài)電流變化而波動(dòng),這是阻抗引起的電源噪聲。

最后,負(fù)載芯片在開(kāi)關(guān)狀態(tài)時(shí)瞬間變化的電流引起的同步開(kāi)關(guān)噪聲(SSN)也是一種電源噪聲。瞬間變化的電流在經(jīng)過(guò)回流途徑上存在的電感時(shí),形成交流壓降,從而產(chǎn)生噪聲,因此也稱(chēng)為?i噪聲。同步開(kāi)關(guān)噪聲主要伴隨器件的同步開(kāi)關(guān)輸出產(chǎn)生,開(kāi)關(guān)速度越快,瞬間電流變化越明顯,電流回路上的電感越大,產(chǎn)生的SSN越嚴(yán)重。因此,SSN并非完全是電源問(wèn)題,其對(duì)電源完整性的影響主要表現(xiàn)為地彈和電源反彈現(xiàn)象。

如何獲得好的PI

想要獲得一個(gè)好的電源供電系統(tǒng),“設(shè)計(jì)+仿真+測(cè)試”,每一步都不能少。

設(shè)計(jì)是基礎(chǔ)

PI(電源完整性)研究的主要內(nèi)容是探討如何確保穩(wěn)壓模塊的輸出能夠通過(guò)傳輸路徑穩(wěn)定地傳遞至負(fù)載的接收端。該研究主要涉及穩(wěn)壓電源和傳輸路徑兩個(gè)核心組成部分。

穩(wěn)壓電源的設(shè)計(jì)是一項(xiàng)涉及眾多因素的復(fù)雜過(guò)程,主要包括以下方面:

1. Power tree設(shè)計(jì)

2. 環(huán)路穩(wěn)定性設(shè)計(jì)

3. 布局布線(xiàn)設(shè)計(jì)

此外還包括電源拓?fù)溥x擇、電源EMI設(shè)計(jì)等等。

傳輸路徑的設(shè)計(jì)也包括很多內(nèi)容,如以下幾點(diǎn):

1. 電源目標(biāo)阻抗設(shè)計(jì)

2. 去耦電容設(shè)計(jì)

3. PCB的疊層設(shè)計(jì)

4. PCB的分割、布局和電源平面分配設(shè)計(jì)

此外還包括地平面處理、電源濾波等等

仿真是手段

如果設(shè)計(jì)是基礎(chǔ),那么仿真就是對(duì)于設(shè)計(jì)的優(yōu)化手段,電源完整性仿真的內(nèi)容很多,主要包括以下幾個(gè)方面:

1. 板級(jí)電源通道阻抗仿真

電源網(wǎng)絡(luò)的目標(biāo)阻抗設(shè)計(jì)要求,是在特定頻率范圍內(nèi)確保電源網(wǎng)絡(luò)的阻抗值不超過(guò)既定目標(biāo)。通過(guò)仿真分析獲得的PDN曲線(xiàn),能夠識(shí)別出阻抗超標(biāo)的頻點(diǎn)或頻段。針對(duì)這些超標(biāo)區(qū)域,可采取添加電容器進(jìn)行去耦的措施,以實(shí)現(xiàn)該頻段阻抗的降低,確保其低于預(yù)設(shè)的目標(biāo)阻抗值。

2. 板級(jí)直流壓降仿真

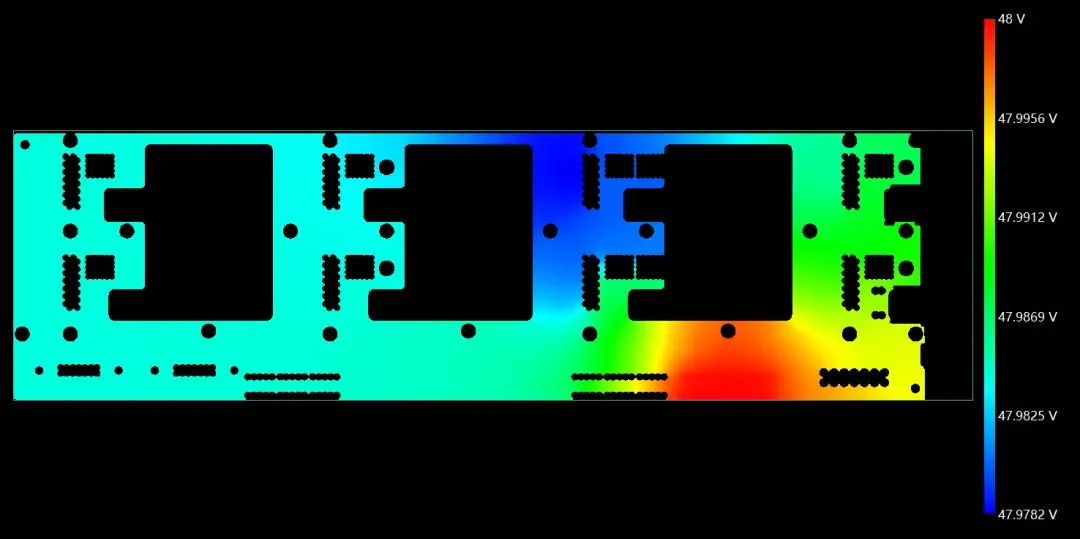

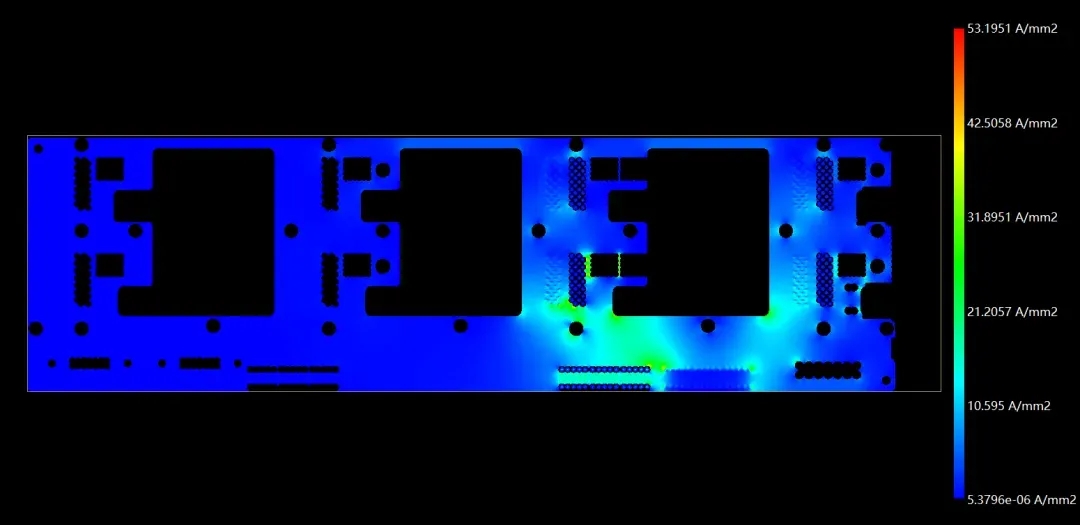

直流壓降(IRdrop)仿真旨在模擬電源平面層的直流電壓降低情況,并分析過(guò)孔及銅皮的電流密度分布與流向,以評(píng)估平面層的載流性能。

芯瑞微(上海)電子科技有限公司的PhysimDC可以針對(duì)電源完整性中直流壓降(IRdrop)進(jìn)行仿真分析,關(guān)注主要仿真電源平面層的直流電壓降,以及過(guò)孔、銅皮的電流密度和電流方向,從而得到平面層的載流能力狀況。通過(guò)監(jiān)測(cè)負(fù)載電流的消耗狀況,可對(duì)各電源平面上點(diǎn)的直流壓降及電流密度進(jìn)行考察,以判斷其是否超出銅皮的載流極限。

PhySim DC電源網(wǎng)絡(luò)電壓分布云圖

PhySim DC電流密度分析

3. 板級(jí)諧振仿真

諧振是指能量被夾在兩個(gè)平行板之間,因原始信號(hào)與其反射信號(hào)同相而形成的共振腔效應(yīng),在諧振頻率點(diǎn)附近,平面對(duì)地阻抗變得很大,將會(huì)導(dǎo)致電源完整性問(wèn)題。另外諧振點(diǎn)若與器件工作頻率相同,將引起共振,共振幅度較大將導(dǎo)致性能下降。

其中平面阻抗和諧振分析稱(chēng)為電源的AC仿真,直流壓降和電流密度仿真為DC仿真。

測(cè)試是檢驗(yàn)

在硬件設(shè)計(jì)領(lǐng)域,測(cè)試是驗(yàn)證設(shè)計(jì)正確性的唯一準(zhǔn)則。由于仿真過(guò)程中可能存在模型與參數(shù)的誤差,測(cè)試成為反映設(shè)計(jì)真實(shí)性的關(guān)鍵環(huán)節(jié)。針對(duì)電源完整性部分的測(cè)試,主要可劃分為以下幾個(gè)主要方面。

1. 紋波、噪聲測(cè)試

紋波與噪聲測(cè)試是電源完整性檢測(cè)的基礎(chǔ)項(xiàng)目。在進(jìn)行此類(lèi)測(cè)試時(shí),以下要點(diǎn)需關(guān)注:

(1)測(cè)試紋波時(shí),通常在電源輸出電容端進(jìn)行;而測(cè)試噪聲時(shí),則在負(fù)載端的濾波電容端進(jìn)行。

(2)測(cè)試紋波與噪聲時(shí),應(yīng)設(shè)置不同的帶寬限制。

(3)采用高比特示波器(如10比特、12比特)以提高測(cè)量精度。

(4)測(cè)試時(shí),應(yīng)選擇示波器最小量程檔位,以獲得最低的本底噪聲。

(5)使用AC耦合或隔直電容可能掩蓋電壓跌落現(xiàn)象或?yàn)V除低頻信號(hào),因此采用DC耦合進(jìn)行測(cè)量至關(guān)重要。若示波器不支持較大偏移量,可使用專(zhuān)業(yè)測(cè)試探頭。

(6)注意設(shè)置輸入阻抗,以降低探頭與示波器構(gòu)成的負(fù)載效應(yīng)。

(7)根據(jù)測(cè)試需求進(jìn)行帶寬限制,并確保接地線(xiàn)盡可能短,以減少外部雜訊干擾。

2. 激勵(lì)響應(yīng)測(cè)試

激勵(lì)-響應(yīng)測(cè)試是通過(guò)向被測(cè)試設(shè)備輸入特定的模擬或數(shù)字信號(hào)作為激勵(lì),并同步收集該設(shè)備的響應(yīng)信號(hào),進(jìn)而通過(guò)對(duì)比分析激勵(lì)信號(hào)與響應(yīng)信號(hào),以檢測(cè)設(shè)備的特性或診斷潛在的故障。在電源完整性測(cè)試的過(guò)程中,測(cè)試人員會(huì)在輸出電壓上利用信號(hào)發(fā)生器疊加任意的激勵(lì)波形,并在負(fù)載端監(jiān)測(cè)傳輸?shù)牟ㄐ危源藖?lái)評(píng)估電源的傳輸質(zhì)量。

3. 環(huán)路穩(wěn)定性測(cè)試

在評(píng)估環(huán)路穩(wěn)定性時(shí),主要方法包括Bode圖法和動(dòng)態(tài)負(fù)載測(cè)試法。對(duì)電源實(shí)施動(dòng)態(tài)負(fù)載測(cè)試,可以用于檢測(cè)環(huán)路穩(wěn)定性。然而,若環(huán)路不穩(wěn)定,為確定問(wèn)題發(fā)生的具體位置,則需采用Bode圖測(cè)試,觀(guān)察增益-相位曲線(xiàn),以進(jìn)行深入分析。

4. PDN測(cè)試

在對(duì)PDN(電源分配網(wǎng)絡(luò))阻抗曲線(xiàn)的仿真正確性進(jìn)行驗(yàn)證時(shí),我們可通過(guò)采用VNA(矢量網(wǎng)絡(luò)分析儀)進(jìn)行實(shí)際測(cè)量,以此對(duì)比仿真結(jié)果與實(shí)測(cè)數(shù)據(jù),分析二者之間的差異。

此外,還包括電壓跌落測(cè)試、電源通道電流測(cè)試等項(xiàng)目。

鑒于電源的穩(wěn)定性是確保產(chǎn)品正常運(yùn)行的關(guān)鍵要素,PI設(shè)計(jì)因此在電子產(chǎn)品開(kāi)發(fā)中占據(jù)著至關(guān)重要的地位。